# **Real-Time Reconnaissance Robot Using FPGA**

Apoorav Gupta<sup>[1]</sup>, Kambhampati Sumant V<sup>[2]</sup>

M.Tech-VLSI Design, School of Electronics Engineering (SENSE), VIT University, Vellore-632014 Tamil Nadu (INDIA) e-mail: apoorav.vit69@gmail.com<sup>[1]</sup>, 92sumant@gmail.com<sup>[2]</sup>

## Abstract

In this project we have Interfaced and Implemented an autonomous vehicle capable of providing a real time RGB and gray scale image of the surrounding search area. We tried to develop an advanced real time image detection method by supporting it with an obstacle avoiding robot as the base. In addition, Sobel Edge Detection algorithm is used to obtain the edge detected version of the RGB image captured by the interfaced camera. This algorithm provides low error rate as compared to other edge detection algorithms. This venture utilizes a 5MP Terasic-DB5M camera to ceaselessly catch a picture stream. Our inspiration emerged from our enthusiasm towards machine vision and dynamics.

**Keywords:** FPGA, Obstacle-Avoider, Sobel-Edge Detection, Real-time Image Capture, Real-time Image Processing.

### Introduction

Image processing and edge detection has always been tedious challenge for researchers across the world. Autonomous machine dynamics plays a very important role in making a device useful for applications such as defense and commercial purposes. The Real time image processing property of our Obstacle Avoider Robot makes it a very outstanding system.

Edge recognition is broadly utilized as a part of picture division to separate a picture into regions comparing to diverse items. Edges happen in parts of the picture with solid power contrast, which regularly speak to question limits. Section II explains about high level designing used. Section III describes about the experiment. Section IV depicts RTL view of the designed system experiment conducted in different arenas for testing. Section V summarizes the results obtained in terms of dynamic power reduction, hardware reduction and failure rate.

(1)

28988

## **High Level Design**

Construction of this search Bot using FPGA uses following main elements:

- 1. Sobel Edge Detection algorithm

- 2. Altera DE2 FPGA Board

- 3. Terasic D5M 5MP camera

- 4. Motor Driver IC L293D.

These hardware components are explained below:

### A. Sobel Edge Detection <sup>[1][2]</sup>

The Sobel Edge recognition Calculation utilizes a 3x3 convolution table to store pixel and its neighbors to compute the subsidiaries. The table is moved over the picture, pixel by pixel. For a 640x480 picture, the convolution table will travel through 302964 (638x478) separate areas in light of the fact that we cannot figure the subsidiary for pixels on the edge of the picture.

The Sobel Edge discovery calculation recognizes both the vicinity of an edge and the course of the edge. There are eight conceivable headings: north, northeast, east, southeast, south, southwest, west, and northwest.

Sobel algorithm consist of Sobel operators<sup>[5]</sup> that are 3x3 convolution masks and works in a two way format i.e- in x-matrix, Gx (vertical direction) and y-matrix, Gy (horizontal direction).The matrices then estimate the gradient in the respective directions and find the edges of the source image, A. The matrices and calculations are shown below-

$$\mathbf{G}_x = \begin{bmatrix} -1 & 0 & +1 \\ -2 & 0 & +2 \\ -1 & 0 & +1 \end{bmatrix} * \mathbf{A} \quad \text{and} \quad \mathbf{G}_y = \begin{bmatrix} +1 & +2 & +1 \\ 0 & 0 & 0 \\ -1 & -2 & -1 \end{bmatrix} * \mathbf{A}$$

The kernels are intended to react maximally to edges running vertically and on a level plane in respect to the pixel network, one portion for each of the two perpendicular introductions. The kernels can be connected independently to the info picture, to deliver separate estimations of the inclination part in every direction (call these Gx and Gy). The gradient is given by:

$$|\mathbf{G}| = \sqrt{(\mathbf{G}\mathbf{x}^2 + \mathbf{G}\mathbf{y}^2)}$$

Sobel Edge detection algorithm is implemented as follows Suppose we have image G(c,r). Gx is given by:

$$Gx = [G(c+1,r-1)+2*G(c+1,r)+G(c+1,r+1)-G(c-1,r+1)-G(c-1,r)-G(c-1,r-1)]; (2)$$

Also, Gy is calculated as

$$Gy = [G(c-1, r-1) + G(c, r-1) + G(c+1, r-1) - G(c-1, r+1) - 2*G(c, r+1) - G(c+1, r+1)]; \quad (3)$$

After obtaining Gx and Gy, their sum provides the gradient magnitude which is compared with threshold value. The pixel is replaced by 1 if the compared value is higher than threshold value otherwise 0 is placed. The same process is repeated for the whole pixel matrix to get the edges.

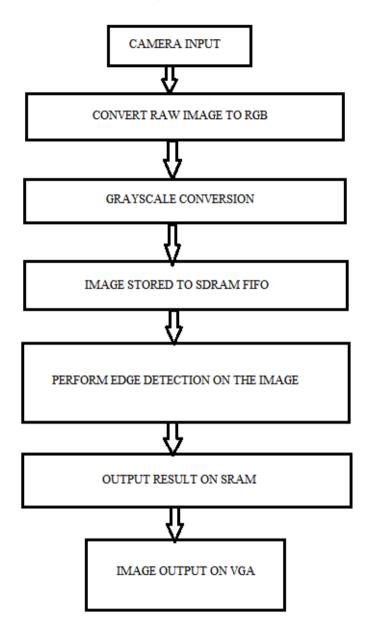

Figure 1: Edge Detection Flowchart

### **B.** Altera DE2 FPGA Board

Altera DE2 board is the suitable hardware that we utilized for designing our project and it includes an Altera Cyclone II EP2C35<sup>[4]</sup> FPGA with 35,000 logic elements (LEs), 8-Mbyte (1-Mbyte x 4 x 16) SDRAM, 4-Mbyte flash memory, a SD card interface, a USB master-slave controller, a 10/100 Ethernet physical layer/media access controller, two serial connectors (RS-232 DB9 ports), etc.

The hardware was designed using the Altera Quartus-II v11.1 software. Other hardware details are given in the following table-

| Specifications         |                   |

|------------------------|-------------------|

| Family                 | Cyclone II        |

| Device                 | EP2C35F672C6      |

| Total Logical Elements | 2161/33216 (7%)   |

| Total Registers        | 1346              |

| Total Memory Bits      | 77728/483840(16%) |

| Total PLL's            | 25%               |

### C. TRDB\_D5M Camera

Terasic TRDB\_D5M 5MP camera is used since it provides a good frame rate, better low light performance and less dark currents.

## D. Motor driver L293D IC

This IC provides two H-bridge<sup>[7]</sup> Transistor circuits thereby offering interfacing with two DC motors simultaneously. This provides our bot a solid movement throughout the surroundings. Pin number 2, 7 and 10, 15 can be used to connect to the motors on either side and then can be driven by giving logics from the FPGA board. Logic 01 and 10 drives motor in clockwise and anti-clockwise direction while logic 00 and 11 stop the motor. This IC has high noise immunity and large supply voltage range. The algorithm used for obstacle avoidance of the robot is given as-

If (sensor output) = 1

Robot=STOP; Delay Robot=Take left or right; Delay Robot= move forward;

Else

Robot= move forward; Delay

End

## **Hardware Interfacing**

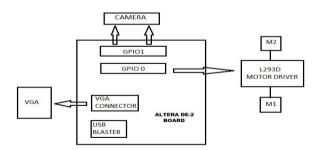

Figure 2: Hardware Interfacing block diagram

#### Real-Time Reconnaissance Robot Using FPGA

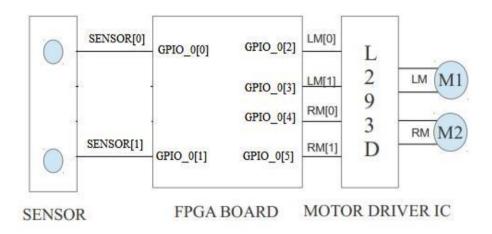

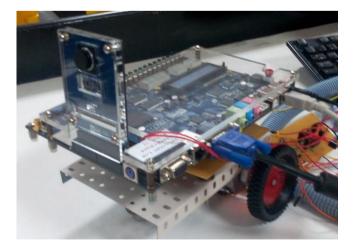

The block diagram in Fig [2] depicts hardware component connections of the project. The various connections to ALTERA DE-2 board have been shown. The camera TRDB D5M is connected to GPIO\_1 whereas the motor driver IC is connected to GPIO\_0 of the FPGA board. The logics are supplied at pin number 2,7 for left motor M1 and 10,15 for right motor M2. The motors are then connected to the motor driver at pin number 3,6(left) and 11,14(right).VGA is connected to the Altera board via VGA connector. USB-Blaster mode of communication is used for downloading the program on the board.

Figure 3: Interfacing diagram

### Experiment

We have conducted several trials for effective edge detection. At first, we showed a still picture on the VGA monitor followed by real time capturization. We also encountered an issue with clock synchronization which was later unraveled by utilizing VGA\_Audio\_Pll to change over Clock\_27 to VGA\_Ctrl\_Clk.

Then we moved on to the edge detection part and realized that lot of images were missed out due to inefficient frame rate. So we used 640 x480 resolution of image and adjusted the camera focus to maximum value under sufficient light condition. After that we set a threshold for gray scale image which increased the gradient and better edge detection results were obtained.

#### Results

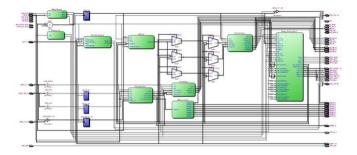

The program for the system was successfully complied and following RTL view Fig-[4] is obtained.

Figure 4: RTL View

The VGA monitor output for the robot is shown below Fig-[6] gives the real-time image of the surroundings while Fig-[6] & [7] shows the gray scale and edge detected images. Different outputs were obtained for different performance parameters such as lighting conditions and gray scale threshold variations.

The Power Play power analysis is done successfully and results obtained showed dissipation power for the given Altera DE-2 board in Figure-5.

| PowerPlay Power Analyzer Status        | Successful - Tue Nov 04 01:35:41 2014                      |

|----------------------------------------|------------------------------------------------------------|

| Quartus II Version                     | 9.1 Build 350 03/24/2010 SP 2 SJ Web Edition               |

| Revision Name                          | DE2_TRDB_SOBEL                                             |

| Top-level Entity Name                  | DE2_TRDB_SOBEL                                             |

| Family                                 | Cyclone II                                                 |

| Device                                 | EP2C35F672C6                                               |

| Power Models                           | Final                                                      |

| Total Thermal Power Dissipation        | 472.64 mW                                                  |

| Core Dynamic Thermal Power Dissipation | 216.50 mW                                                  |

| Core Static Thermal Power Dissipation  | 81.16 mW                                                   |

| I/O Thermal Power Dissipation          | 174.98 mW                                                  |

| Power Estimation Confidence            | Medium: user provided moderately complete toggle rate data |

|                                        |                                                            |

## Figure 5: Power Play Power Analysis

Figure 6: RGB image

Figure 7: Gray Scale image

Figure 7: Edge Detected Image

Figure 8: Reconnaissance Robot

### 28994

## Conclusion

In the final phase Obstacle avoidance robot was designed and tested in the lab for search operation and images of the surroundings were obtained on the VGA monitor in both gray scale and edge-detection mode.

## References

- [1] "A Descriptive Algorithm for Sobel Image Edge Detection", O. R. Vincent, Clausthal University of Technology, Germany, O. Folorunso, University of Agriculture, Abeokuta, Nigeria. Proceedings of Informing Science & IT Education Conference (InSITE) 2009.

- [2] "A Classified and Comparative Study of Edge Detection Algorithms" by Mohsen Sharifi, Mahmoud Fathy, Maryam Tayefeh Mahmoudi Department of Computer Engineering, Iran University of Science and Technology. Proceedings of the International Conference on Information Technology: Coding and Computing (ITCC.02) 2002 IEEE

- [3] "Rapid Prototying of Digital Systems-SOPC Edition"-by James O. Hamblen, Tyson S. Hall, Michael D. Furman.

- [4] "DE2 Development and Education Board-User Manual" by ALTERA

- [5] Sobel Operator, http://en.wikipedia.org/wiki/Sobel\_operator.

- [6] Embedded Core Design using FPGA's by Zainalabedin Navabi.

- [7] Embedded design Handbook by ALTERA.

- [8] L293, L293D Quadruple H-Drivers Datasheets by Texas Instruments.

- [9] Design and Implementation of Line Follower Robot using FPGAS by Shravya K V, Kevin Kansagara, Sivasankara.K